跳票数年,英特尔10nm终现身:SuperFin重新定义晶体管架构,节点内性能提升超过15%

编者按:本文来自微信公众号“机器之能”(ID:almosthuman2017),作者:微胖、徐丹,36氪经授权发布。

SuperFin是英特尔10nm最大的亮点,它是FinFET结构的升级版。英特尔将增强型FinFET晶体、Super MIM(金属-绝缘体-金属)电容器相结合,打造了全新的SuperFin,能够提供增强的外延源极/漏极、改进的栅极工艺,额外的栅极间距。

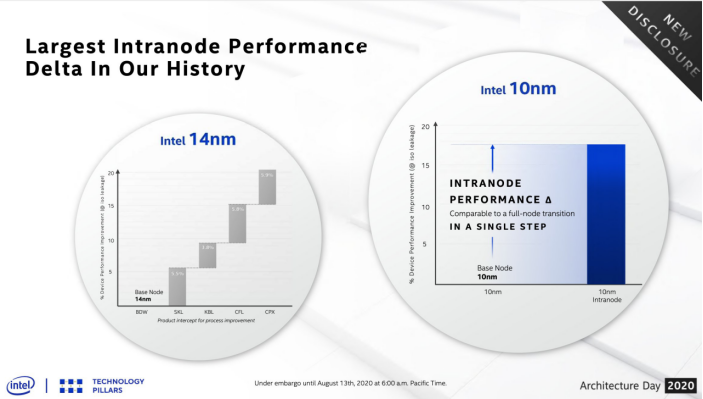

英特尔表示,这是该公司有史以来最为强大的单节点内性能增强,10nm工艺可以实现节点内超过15%的性能提升,带来的性能提升可与全节点转换相媲美。」换言之,在SuperFin技术的加持下,英特尔推出的10nm工艺效能可以等同于7nm。

有时,好事如同正义,虽会迟到,但还是会来。

本周二,英特尔的顶级工程师们罕见揭开“跳票”已久的Tiger Lake 10nm CPU微架构面纱,后者将出现在9月2日发布的产品中。设计师们为这款即将面世的Tiger Lake感到骄傲,不过仍被禁止讨论处理器性能。

这款被称为英特尔第11代CPU的处理器,将与Xe Graphics 配对使用,并惠及服务器到游戏的所有生态成员。英特尔首席架构师拉贾·科杜里(Raja Koduri)表示,他们还将采用 SuperFin 技术。

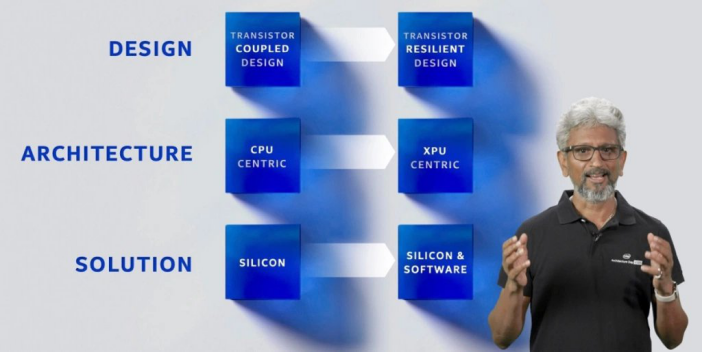

英特尔的处理器设计方法。

自从不得不推迟7纳米制造工艺之后,英特尔也不断经历着挣扎。今年早些时候,英特尔首席财务官乔治 · 戴维斯(George Davis)在摩根士丹利 3 月的会议上对投资者承认,公司已经落后于竞争对手台积电,要追赶上至少需要 2 年时间。

本月,原首席工程官 Venkata Renduchintala辞职。更早的时候,著名芯片架构师吉姆·凯勒因个人原因离开英特尔。

事实上,英特尔盯紧7nm,也与10nm制程多次延期有关,希冀借此弥补10nm延期所造成的时间损失。如今看来,还是10 nm 最先守得云开见月明,未来几年,10nm 也将代表英特尔最佳工艺水平。

一 英特尔的挣扎:多次跳票的10nm

早在 2013 年,英特尔就设想通过 2.7 倍密度的 SAQP、COAG、Cobolt 互连,以及 EMIB 和 Foveros 等新的封装技术,让 10nm 芯片成功接过 14nm 芯片接力棒。

然而,在将10纳米技术推向市场时遭遇延误,并一再跳票。

最初,10nm工艺安排在2016年下半年,但是,2015年初,英特尔就推迟相关制造设备的安装部署。当年7月,公司承认大规模量产推迟到2017年下半年,并临时增加 Kaby Lake(七代酷睿),号称工艺优化升级为14nm+。

随后,Intel规划了基本完整的10nm产品线,包括面向低功耗桌面和移动市场的Cannon Lake、针对高端桌面和服务器的Ice Lake、配合新工艺升级架构的的Tiger Lake。

2017年初CES大展上,Intel首次展示了配备Cannon Lake处理器的笔记本,并保证会在当年晚些时候发布,但 Ice Lake、Tiger Lake都推迟到了2018年。Intel不得不又增加Coffee Lake(八代酷睿),工艺再次优化为14nm++。

2018年4月,公司宣布由于良品率问题,10nm工艺大规模量产将推迟到2019年。

2019年初,英特尔在CES上正式公布10nm 制程落地并披露更多相关细节。

对于长达数年的“跳票“,英特尔给出的解释包括设想太自信、团队之间目标不明确、管理混乱以至于计划一拖再拖。事实上,也与英特尔IDM模式有关。

英特尔是为数不多的IDM垂直整合型半导体公司。自己设计芯片架构、自己制造芯片、自己封装芯片,其它芯片厂商几乎做不到。

这种模式的好处很明显,英特尔能够自主根据不同工艺开发不同的CPU架构。因为全自主,新工艺开发的架构可以最大化利用特定工艺优势,达到更好的匹配与契合。

但不足之处在于,将架构与工艺捆绑起来制约了灵活性。比如10nm延期之后,英特尔无法使用14nm工艺去生产10nm制程架构就是典型的例子。

如今,英特尔10nm 终见曙光,彼时的三星、台积电早就有10nm,并已开始量产7nm。当然,各家工艺技术不同,没有直接可比性。

英特尔表示,自家 14nm、10nm、7nm 分别相当于台积电的 10nm,7nm、5nm。至少从字面看,英特尔在10nm制程节点已经做到与台积电7nm制程同样的晶体管集成数量,但是,性能究竟如何,仍然是用户和市场说了算。

二 节点内超过15%的性能提升,SuperFin重新定义FinFET

姗姗来迟的10nmCPU也没有让市场空等,10nm CPU创新性的使用了Super Fin工艺。

几年前,英特尔首应用了22nm FinFET工艺,可以说是晶圆制造历史上的一次重要革命。

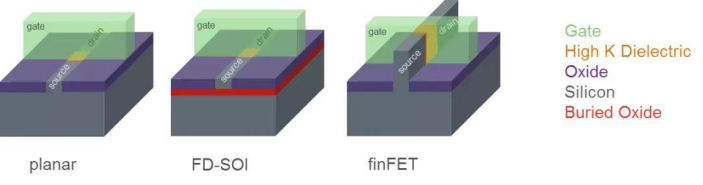

FinFET是晶圆制造工艺的一种,称为鳍式场效应晶体管(Fin Field-Effect Transistor),其中的Fin在构造上与鱼鳍非常相似,所以称为“鳍式”,而FET的全名是“场效电晶体” 。

FinFET的变革性意义在于将传统晶体管的2D结构变为3D架构。传统晶体管结构是平面的,所以只能在闸门的一侧控制电路的接通与断开。但是在FinFET架构中,闸门被设计成类似鱼鳍的叉状3D架构,可于电路的两侧控制电路的接通与断开。这种叉状3D架构不仅能改善电路控制和减少漏电流,同时让晶体管的闸长大幅度缩减。

但FinFET工艺制造及其复杂,在英特尔的改良应用之下,台积电、三星等厂商才后续跟上。不过随着制程的发展,FinFET也需要改良。

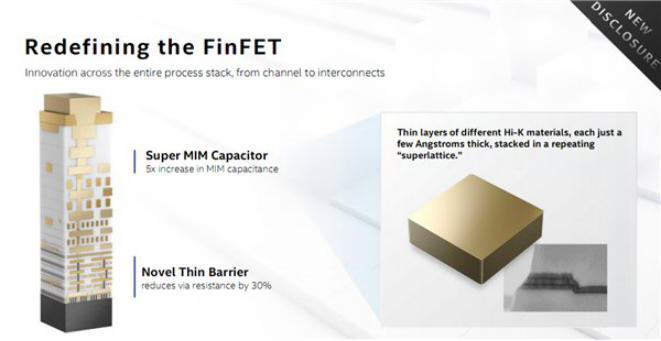

昨日英特尔的披露的下一代Willow Cove CPU升级了FinFET,它将增强型FinFET晶体、Super MIM(金属-绝缘体-金属)电容器相结合,打造了全新的SuperFin,能够提供增强的外延源极/漏极、改进的栅极工艺,额外的栅极间距。

英特尔官方显示,与FinFET相比,SuperFin架构性能主要优势体现在如下方面:

1、增强源极和漏极上晶体结构的外延长度,从而增加应变并减小电阻,以允许更多电流通过通道。

2、改进栅极工艺,以实现更高的通道迁移率,从而使电荷载流子更快地移动。

3、提供额外的栅极间距选项,可为需要最高性能的芯片功能提供更高的驱动电流。

4、使用新型薄壁阻隔将过孔电阻降低了30%,从而提升了互连性能表现。

5、与行业标准相比,在同等的占位面积内电容增加了5倍,从而减少了电压下降,显著提高了产品性能。

该技术的实现主要得益于一类新型的高K电介质材料,它可以堆叠在厚度仅为几埃米(也就是零点几纳米)的超薄层中,从而形成重复的“超晶格”结构。这也是Intel独有的技术。

「这是该公司有史以来最为强大的单节点内性能增强,10nm工艺可以实现节点内超过15%的性能提升,带来的性能提升可与全节点转换相媲美。」换言之,在SuperFin技术的加持下,英特尔推出的10nm工艺效能可以等同于7nm。

英特尔称,10nm SuperFin晶体管技术将在代号Tiger Lake的下一代移动酷睿处理器中首发,现已投产,OEM笔记本将在今年晚些时候的假日购物季上市。

三 发布游戏专用GPU架构,与英伟达、AMD一较高下?

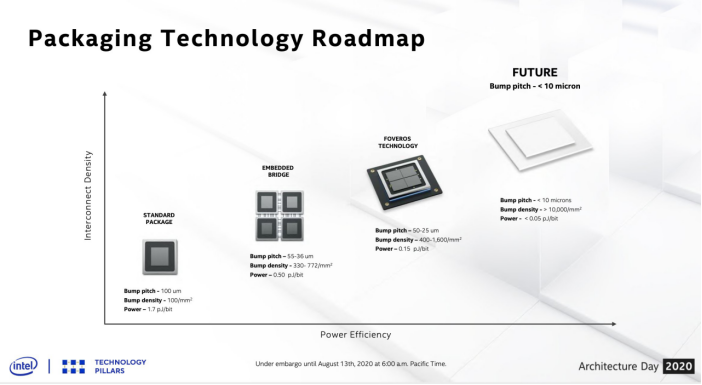

除SuperFin架构,英特尔也披露了“混合结合(Hybrid bonding)”这一先进封装技术。

如今异构已经成了未来芯片发展的一种趋势,越来越多的硬件甚至IP将会集成到一块芯片当中。英特尔提出的封装技术实际上就相当于一种分解设计,化繁为简,芯片分为CPU、GPU、IO等,再分别更新或验证,这样就可以避免CPU和GPU纠缠一起出现bug的问题。

要达到这种设计效果,其中的互联就变得尤为重要,“混合结合”解决的就是分解设计中的互联问题,能够加速实现10微米及以下的凸点间距,提供更高的互连密度、带宽和更低的功率。

据透露,使用“混合结合(Hybrid bonding)”技术的测试芯片已在2020年第二季度流片。

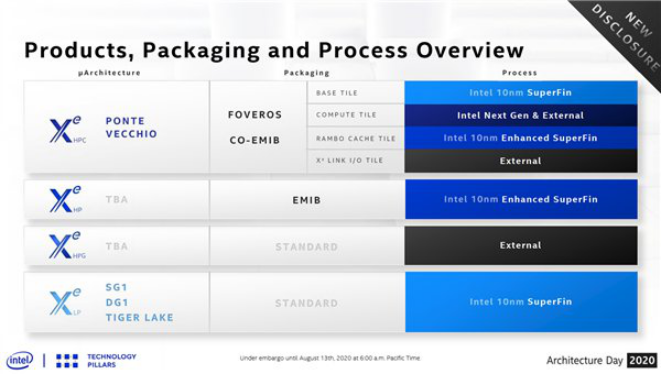

英特尔的这些技术都在下一代酷睿处理器Tiger Lake中体现。据英特尔透露,Tiger Lake将由英特尔全新的Willow Cove架构提供动力,Willow Cove就是基于10nm的SuperFin技术。

英特尔指出,Tiger Lake将在关键计算矢量方面提供智能性能和突破性进展。它是英特尔第一个采用全新 Xe-LP微架构的SoC架构,可以对CPU、AI加速器进行优化,在AI性能、图形性能上有所提升。

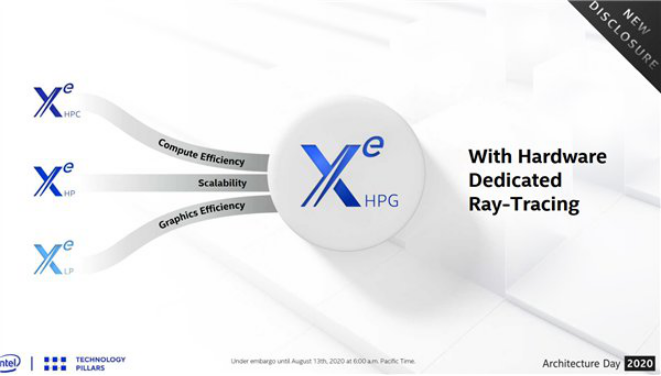

Xe-LP是Intel面向PC和移动计算平台的最高效架构,拥有多达96个EU,并采用了包括异步计算在内的新架构设计,以提供更大的动态范围和频率提升。Xe-LP之外,英特尔还推出了其他两款架构版本,Xe-HP和Xe-HPG。

据介绍 Xe-HP面向数据中心市场,是业界首个多区块(multi-tiled)、高度可扩展的高性能架构,可提供数据中心级、机架级媒体性能,GPU可扩展性和AI优化。它涵盖了从一个区块(tile)到两个和四个区块的动态范围的计算,其功能类似于多核GPU,有望在2021年发布。

Xe-HPG专门针对游戏而设计,添加了基于GDDR6的新内存子系统以提高性价比,新增了游戏及时调整和游戏锐化两个新功能,同样预计同样在2021年发布。值得注意的是,这可能代表着英特尔将首次围绕游戏所需的GPU,意味着英特尔打算在这个领域AMD、英伟达一较高下。

所以现在Xe GPU的架构就变成了Xe LP、Xe HPG、Xe HP及Xe HPC四大金刚了,未来会覆盖核显到HPC超算在内的多个场景。

除了Tiger Lake之外,英特尔还在本次发布会中提到了另外一款产品——Alder Lake。据介绍,该产品是英特尔的下一代采用混合架构的客户端产品。Alder Lake将结合英特尔即将推出的两种架构——Golden Cove和Gracemont,并将进行优化,以提供出色的效能功耗比。

软件oneAPI Gold版本将于今年晚些时候推出,为开发人员提供在标量、矢量、距阵和空间体系结构上保证产品级别的质量和性能的解决方案。

四 10nm能拯救英特尔吗?

英特尔芯片制造工艺的挤牙膏很大程度上拖累了芯片上市进程。英特尔表示正在尝试改变其芯片设计与制造的结合方式,暗示它可以使用外部制造商(例如合同芯片制造商台积电)来制造其芯片。

Koduri将此新策略称为“系统弹性设计”。此前有消息传出英特尔已经在台积电下了不少订单,不过,是GPU订单。

从Super Fin工艺的推出来看,英特尔还是会把CPU制造紧紧的抓在自己手里,并且作为一大核心优势。

从目前披露出的性能看,英特尔的10nm Super Fin架构的确在技术上前进了不小的一步。但有业内人士认为,相比它的竞争对手们,英特尔还是迟了,即便在SuperFin的加持下,10nm也只能是达到7nm的技术水平。

最大的不确定性在于,英特尔目前的技术进展还处于“PPT阶段”,市场上还没有任何英特尔10nm产品的消息。

那么,在Super Fin加持的英特尔10nm是否能如期上市,上市表现究竟会如何?还得等市场验证。

参考资料

https://venturebeat.com/2020/08/13/intels-chip-architects-promise-innovations-despite-setbacks/